OMAPL132

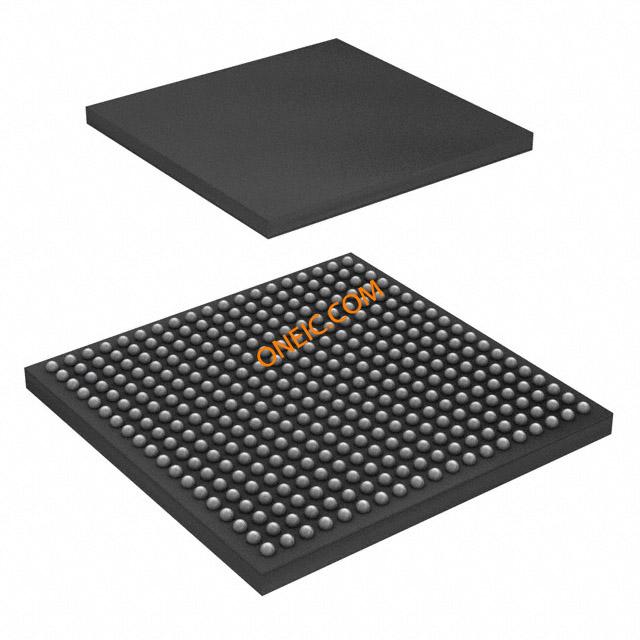

High-performance DSP and ARM processors in 361-pin NFBGA packages

Manufacturer: ti

series introduction

# OMAPL132 Product Series Introduction

## 1. Overview

The OMAPL132 is a highly versatile and powerful system - on - chip (SoC) product series developed by Texas Instruments. It combines a high - performance ARM926EJ - S core with a TMS320C674x floating - point digital signal processor (DSP) core, offering a unique blend of general - purpose computing and digital signal processing capabilities. This makes it an ideal choice for a wide range of applications that require both efficient control and high - speed signal processing.

## 2. Key Features

### 2.1 Processor Cores

- **ARM926EJ - S Core**:

- The ARM926EJ - S core operates at a clock speed of up to 300 MHz. It provides a rich set of instruction sets and a high - performance architecture for general - purpose computing tasks. This core is well - suited for tasks such as running operating systems, handling user interfaces, and managing system resources. It supports a variety of operating systems, including Linux, making it easy for developers to build complex software applications.

- It has a 5 - stage pipeline and a Harvard architecture, which allows for efficient instruction fetch and execution. The core also includes a memory management unit (MMU), enabling virtual memory management and providing better security and isolation for different software components.

- **TMS320C674x DSP Core**:

- The TMS320C674x floating - point DSP core runs at up to 456 MHz. It is designed for high - speed digital signal processing tasks, such as audio and video processing, image processing, and communication signal processing. The DSP core has a very high computational throughput, with a peak performance of up to 3.648 billion floating - point operations per second (GFLOPS).

- It features a very long instruction word (VLIW) architecture, which allows it to execute multiple instructions in parallel, further enhancing its processing efficiency. The DSP core also has a large on - chip memory, including program and data caches, which reduces the memory access latency and improves the overall performance.

### 2.2 Memory and Storage

- **On - Chip Memory**:

- The OMAPL132 has a significant amount of on - chip memory, including 128 KB of L2 memory that can be configured as cache or scratch - pad memory. This on - chip memory provides fast access to data and instructions, reducing the need for external memory access and improving the system's performance.

- **External Memory Interfaces**:

- It supports a variety of external memory interfaces, such as SDRAM, DDR SDRAM, and NAND Flash. The SDRAM interface allows for the connection of high - speed synchronous dynamic random - access memory, which is suitable for storing large amounts of data and running memory - intensive applications. The NAND Flash interface enables the use of non - volatile storage for storing the operating system, application code, and user data.

### 2.3 Peripherals

- **Communication Peripherals**:

- **Ethernet**: The OMAPL132 includes an Ethernet MAC (Media Access Controller) with support for 10/100 Mbps Ethernet. This allows the device to be easily connected to local area networks (LANs) for data communication, remote monitoring, and network - based control applications.

- **UART**: It has multiple universal asynchronous receiver - transmitters (UARTs), which are commonly used for serial communication with other devices, such as sensors, actuators, and modems. The UARTs support a wide range of baud rates, making them flexible for different communication requirements.

-

Images for reference

361-NFBGA

Image Preview

Image Preview